概要

東京工業大学大学院理工学研究科の松澤昭教授と岡田健一准教授らの研究グループは、アナログデジタル変換器(ADC)[用語1]を用いた新方式のデジタルクロック生成器の開発に成功した。従来のデジタルPLL[用語2]に比べ、低消費電力かつ低ジッタ[用語3]で動作することを確認した。

位相同期を電圧差の検出によって行うという新たな発想に基づき、発振器出力を直接、標本化する電圧サブサンプリング技術により実現した。従来のデジタルPLLは位相同期のために時間差検出による帰還(フィードバック)制御を行っていたが、時間差検出の分解能を高くできないことが課題だった。新技術はこの課題を解決する成果である。

最小配線半ピッチ65nm(ナノメートル)のシリコンCMOSプロセスで試作した新型デジタルPLLは、2.2GHz(ギガヘルツ、1Gは10億)のクロックを生成可能であり、クロックの揺れが発振周期の0.08%と非常に良好なジッタ特性を達成した。消費電力は4.2mWと低い。この技術が実用化されれば、身のまわりのあらゆる電子機器に超小型バッテリーレスセンサーを組み込むことが可能となる。

研究成果は22日から米国サンフランシスコで開かれた「ISSCC (国際固体回路国際会議)」で、25日に発表された。

研究の背景・意義

クロック生成回路は、あらゆる電子機器に必要な基盤要素回路であり、低ジッタかつ低消費電力であることが求められる。デジタル回路用のクロックのほか、無線通信・有線通信やデータコンバータ用のクロックとして用いられる。クロック生成には、通常、位相同期回路(PLL : Phase-Locked Loop)を用いる。従来のアナログ方式のPLLでは、フィルタの面積が大きいことが問題であり、この問題を解決するため、近年、デジタルフィルタを用いるデジタルPLLが盛んに研究されている。

デジタルフィルタにすることで、フィルタ部分の面積が小さくでき、所望周波数に達するまでのロック時間を短くすることができる。デジタルPLLでは、発振器の出力を分周した信号と基準信号との時間差を検出する時間差デジタル変換器(TDC : Time-to-Digital Converter)[用語4]を用いる。

帰還ループをデジタル化することで、柔軟かつ堅牢な制御が可能である一方で、TDCの時間分解能があまり高くできないことが原因でジッタが劣化するのが問題点である。TDCの時間分解能が荒いと、帯域内位相雑音[用語5]が劣化し、結果として、ジッタが大きくなる。

研究成果

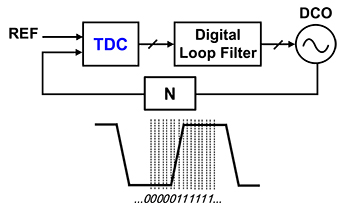

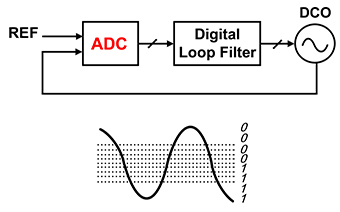

松澤教授と岡田准教授らはTDCの代わりに、ADC(Analog-to-Digital Converter)を用いることで解決を試みた。時間差を検出するよりも、電圧差の方が高精度で検出できることに基づく回路構成である。つまり、従来のデジタルPLLではTDCを用いていたが、新規デジタルPLLではADCを用いることにより、低ジッタかつ低消費電力な特性を可能とした(図1)。分周器を用いない電圧サブサンプリングにより実現した。

Clik here to view.

(a)TDCによるPLL(従来型)

Clik here to view.

(b)ADCによるPLL(提案型)

図1. デジタルPLLの校正

特徴:デジタル型位相同期回路(PLL)において、従来は時間デジタル変換器(TDC : Time-to-Digital Converter)が用いられていたが、提案型ではアナログデジタル変換器(ADC : Analog-to-Digital Converter)を用いることにより、非常に良好なジッタ特性の実現が可能である。

時間軸処理に対する電圧軸処理の利点は、(1)容量により電圧値をサンプリングできる、(2)正確に線形な電圧増幅ができる、(3)ジッタを減らすのに、余分な電力が不要、(4)ばらつきや電源電圧・温度変化などにより基準電圧範囲が変動しない、(5)抵抗ラダー(抵抗をはしご形に接続した回路)などにより容易に中間の電圧値を生成できることである。

これらの特徴により、電圧差による位相検出の方が、より高分解能かつ低消費電力な特性を実現できる(表1)。デジタルPLLにこのADCによる位相検出器を用いれば、非常に低い帯域内位相雑音かつ低ジッタ特性の実現が可能となる。消費電力も低くできる。

表1. TDC型デジタルPLL(従来)とADC型デジタルPLL(本技術)の特徴比較

特徴:位相比較器としてADC型では高い分解能および線形性を実現でき、PLLとして非常に低い帯域内位相雑音かつ低ジッタ特性の実現が可能。消費電力も低い。

(従来技術) TDCを用いた時間差→デジタル変換 |

(本技術) ADCを用いた電圧差→デジタル変換 |

|

|---|---|---|

線形性 |

悪い |

非常に高い |

分解能 |

普通 |

高い |

消費電力 |

内部ジッタを抑えるために大電力が必要 |

低い |

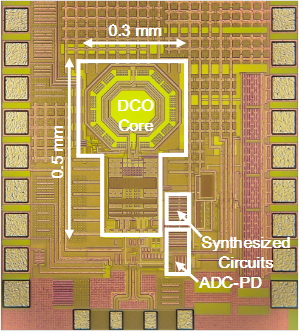

ADCを用いた新規デジタルPLLを、最小配線半ピッチ65nm(ナノメートル)のシリコンCMOSプロセスで試作した。図2にチップ写真を示す。表2にTDC型のデジタルPLLとの比較を示す。本開発品は、4.2mWの消費電力を用い、2.2GHzの周波数で発振する。帯域内位相雑音は-112dBc/Hzと非常に良好であり、クロックの揺れを表すジッタ特性は、RMS値で380fsであり、発振周期に対して0.08%と、非常に良好である。ジッタを消費電力で正規化したPLL FoM[用語6]特性において非常に良好な特性を実現した(低いほど良好)。

Clik here to view.

図2. チップ写真

特徴:CMOS 65nmプロセスにより製造した。

表2. 従来のTDC型PLLとの性能比較

特徴:ADC型は位相分解能が高く、帯域内位相雑音を低減できるため、低ジッタ特性を実現できる。消費電力も低い。 ジッタを消費電力で正規化したPLL FoM特性において非常に良好な特性を実現した(低いほど良好)。

本研究 |

C. Hsu JSSC'09 |

C.Yao JSSC'13 |

Chilara ISSCC'14 |

|

|---|---|---|---|---|

方式 |

ADC-based |

TDC-based |

TDC-based |

TDC-based |

周波数 |

2.2GHz |

3.6GHz |

2.7GHz |

2.4GHz |

RMSジッタ |

380fs |

200fs |

230fs |

1.71ps |

帯域内位相雑音 |

-112dBc/Hz |

-107dBc/Hz |

-110dBc/Hz |

-90dBc/Hz |

PLL FoM |

-242dB |

-237dB |

-240dB |

-236dB |

消費電力 |

4.2mW |

47mW |

17mW |

0.9mW |

面積 |

0.15mm2 |

0.95mm2 |

0.62mm2 |

0.20mm2 |

今後の展開

松澤教授と岡田准教授らが開発したADC型PLLは、従来、不可能であった低消費電力かつ低ジッタ特性を同時に達成するものである。無線機の小型・低消費電力化、マイクロプロセッサや専用LSIの大幅な低消費電力化・高速化・小型低価格化に威力を発揮する技術といえる。超小型バッテリーレスセンサーなどあらゆる機器に組み込むことが期待される。

発表予定

この成果は、2月22日~26日にサンフランシスコで開催された「2015 IEEE International Solid-State Circuits Conference(ISSCC 2015): 2015年IEEE 国際固体回路国際会議」のセッション「Session 25 ? RF Frequency Generation from GHz to THz」で発表された。講演タイトルは「A 2.2GHz -242dB-FOM 4.2mW ADC-PLL Using Digital Sub-Sampling Architecture(ADCを用いたサブサンプリングPLL)」である。現地時間2月25日午後2時から発表された。

用語説明

[用語1] アナログデジタル変換器(ADC : Analog-to-Digital Converter) : 入力されたアナログ値をデジタル値に変換する変換器。

[用語2] 位相同期ループ (PLL : Phase-Locked Loop) : 集積回路中では正確な周波数基準が作れないため、水晶発振器による基準周波数frefを用い、それをN逓倍して所望周波数N・frefの周波数の信号を得る。PLLには、位相周波数比較器、チャージポンプ、ローパスフィルタを用いるアナログPLLと、時間差デジタル変換器(TDC)とデジタルローパスフィルタを用いるデジタルPLLが知られている。

[用語3] ジッタ : クロックの重要な特性の一つで、クロック信号の立ち上がりまたは立ち下りタイミングが揺らぐ現象で、本来のタイミングからのずれが統計的にどれぐらいの幅を持つかで評価する。ジッタが小さいほど、クロックの揺らぎが小さい状況を示す。クロックを生成している発振器の位相雑音特性に大きく依存し、位相雑音が低いほど、ジッタも小さくなる。

[用語4] 時間差デジタル変換器(TDC : Time-to-Digital Converter) : 二つのデジタル入力信号の立ち上がりの時間差、もしくは、立ち下がりの時間差をデジタル値に変換する変換器。時間デジタル変換器とも呼ばれる。

[用語5] 位相雑音 : 発振器の重要な特性の一つ。必要な周波数の信号に対し,どれだけ不要な周波数のスペクトルを持つかを表す。

[用語6] FoM : FoM(Figure of Merit)の略で、消費電力で規格化したジッタ性能を示す。ジッタと消費電力はトレードオフの関係にあり、発振器の消費電力を増やすとジッタが減少し、消費電力を減らすとジッタが増加する。

FoMは、ジッタの標準偏差(σt)と消費電力PDCを用いて、以下の式で定義される。

Image may be NSFW.

Clik here to view.

ジッタ特性が同じでFoMが10dB小さければ、消費電力が10分の1であることに相当する。

論文情報

掲載誌 : |

2015 IEEE International Solid-State Circuits Conference(ISSCC 2015): 2015年IEEE 国際固体回路国際会議 |

論文タイトル : |

A 2.2GHz -242dB-FOM 4.2mW ADC-PLL Using Digital Sub-Sampling Architecture(ADCを用いたサブサンプリングPLL) |

著者 : |

Teerachot Siriburanon(博士課程学生), Satoshi Kondo(近藤智史:修士課程卒業生), Kento Kimura(木村健将:修士課程学生), Tomohiro Ueno(上野智大:修士課程卒業生), Satoshi Kawashima(川嶋理史:修士課程学生), Tooru Kaneko(金子徹:修士課程学生), Wei Deng(博士課程卒業生), Masaya Miyahara(宮原正也:助教), Kenichi Okada(岡田健一:准教授), and Akira Matsuzawa(松澤昭:教授)

|

問い合わせ先

東京工業大学大学院理工学研究科電子物理工学専攻

准教授 岡田健一

Email : okada@ssc.pe.titech.ac.jp

Tel : 03-5734-2258

Fax : 03-5734-3764

- ※

- 3月10日13:30 表1の項目名に誤りがありましたので、修正しました。